Hindawi Publishing Corporation Abstract and Applied Analysis Volume 2012, Article ID 726927, 7 pages doi:10.1155/2012/726927

## Research Article

# A Chaotic Attractor in Delayed Memristive System

## Lidan Wang<sup>1,2</sup> and Shukai Duan<sup>1</sup>

<sup>1</sup> School of Electronic and Information Engineering, Southwest University, Chongqing 400715, China

Correspondence should be addressed to Shukai Duan, duansk@swu.edu.cn

Received 21 September 2012; Accepted 13 October 2012

Academic Editor: Chuandong Li

Copyright © 2012 L. Wang and S. Duan. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Over the last three decades, theoretical design and circuitry implementation of various chaotic generators by simple electronic circuits have been a key subject of nonlinear science. In 2008, the successful development of memristor brings new activity for this research. Memristor is a new nanometre-scale passive circuit element, which possesses memory and nonlinear characteristics. This makes it have a unique charm to attract many researchers' interests. In this paper, memristor, for the first time, is introduced in a delayed system to design a signal generator to produce chaotic behaviour. By replacing the nonlinear function with memristors in parallel, the memristor oscillator exhibits a chaotic attractor. The simulated results demonstrate that the performance is well predicted by the mathematical analysis and supports the viability of the design.

#### 1. Introduction

The memristor, characterized by a relation of the type  $f(\varphi,q)=0$ , is a nanometer-scale circuit element postulated by Chua in 1971 [1] on the basis of the conceptual symmetry between the resistor, inductor, and capacitor. After 37 years a team at HP Labs announced [2] the first physical realization of a memristor and a mathematical model accounting for its behavior. This missing memristor is a new nanometer-size two-terminal circuit element characterized by a relationship between charge and flux. The resistance of memristor is proportional to the amount of charge that has passed through it. So, in a way, it possesses memory, which has caused tremendously increased interests. Recently many researchers worked actively on the memristor models and possible applications of the device [3]. For interpreting and understanding the principle and structure of memristor, people discuss theoretical models from different angles.

Theoretical design and circuitry implementation of various chaotic generators by simple electronic circuits have been a key subject of nonlinear science [4]. To enhance degree

<sup>&</sup>lt;sup>2</sup> College of Computer Science, Chongqing University, Chongqing 400044, China

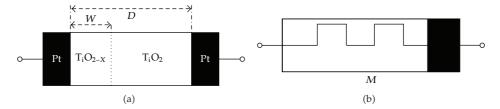

Figure 1: Structure (a) and symbol (b) of T<sub>i</sub>O<sub>2</sub> memristor.

of chaos, a nonlinear part in a chaotic circuit, which is frequently implemented by operational amplifiers, becomes more and more complex. Considering the nanoscopic scale size and the nonlinear characteristics of memristor, more rich chaotic behaviors should be generated if replacing the nonlinear circuit with memristor. Itoh and Chua [5] initially derive several nonlinear oscillators from Chua's oscillators by replacing Chua's diodes with memristors. Recently a lot of papers on memristive chaotic circuit have been reported [6–10]. Because of its small size and nonlinearity, memristor is very suitable for chaotic oscillators [11]. In this paper, a delayed system utilizing  $T_iO_2$  memristors as nonlinear function is proposed to generate chaotic signals.

### 2. T<sub>i</sub>O<sub>2</sub> Memristor with Linear Dopant Drift

In HP's memristor, a titanium dioxide  $(T_iO_2)$  layer and an oxygen-poor titanium dioxide  $(T_iO_{2\geq x})$  layer are sandwiched between two platinum electrodes, shown as Figure 1. Let D be the physical length of the memristor,  $\mu_V = 10^{-14}\,\mathrm{m^2 s^{-1} V^{-1}}$  is the dopant mobility,  $R_{\mathrm{ON}}$  and  $R_{\mathrm{OFF}}$  are the low resistance and higher resistance areas, respectively. The electrical characteristics of the memristor with linear dopant drift from [1] are given by (2.1):

$$M(t) = R_{\rm ON} \frac{\omega(t)}{D} + R_{\rm OFF} \left[ 1 - \frac{\omega(t)}{D} \right], \tag{2.1}$$

where  $\omega(t)$  is the width of dopant region bounded between zero and D, which its derivative is

$$\dot{\omega}(t) = \frac{\mu_V R_{\rm ON}}{D} i(t). \tag{2.2}$$

According to the Bernoulli dynamics, we can derive the relation between the charge and magnetic flux as follows [5]:

$$q(t) = \begin{cases} \frac{\varphi(t) - c_1}{R_{\text{OFF}}}, & \varphi(t) < c_3, \\ \frac{\sqrt{2k\varphi(t) + M^2(0)} - M(0)}{k}, & c_3 \le \varphi(t) < c_4, \\ \frac{\varphi(t) - c_2}{R_{\text{ON}}}, & \varphi(t) \ge c_4, \end{cases}$$

(2.3)

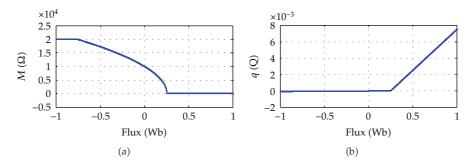

**Figure 2:** The  $M - \varphi$  and  $q - \varphi$  characteristics of memristor.

where

$$c_{1} = -\frac{\left[R_{\text{OFF}} - M(0)\right]^{2}}{2k}$$

$$c_{2} = -\frac{\left[R_{\text{ON}} - M(0)\right]^{2}}{2k}$$

$$c_{3} = \frac{R_{\text{OFF}}^{2} - M^{2}(0)}{2k}$$

$$c_{4} = \frac{R_{\text{ON}}^{2} - M^{2}(0)}{2k},$$

(2.4)

k is a constant  $k = (R_{\rm ON} - R_{\rm OFF})\mu_V R_{\rm ON}/D^2$ , and  $\omega_0$  and M(0) are the initial conditions of  $\omega(t)$  and M(t), respectively. The resistance of memristor is

$$M(t) = \begin{cases} R_{\text{OFF}}, & \varphi(t) < c_3 \\ \sqrt{2k\varphi(t) + M^2(0)}, & c_3 \le \varphi(t) < c_4 \\ R_{\text{ON}}, & \varphi(t) \ge c_4, \end{cases}$$

(2.5)

Figure 2 shows the characteristics of memristor when parameters are chosen by  $R_{\rm ON}=100\,\Omega$ ,  $R_{\rm OFF}=20\,{\rm k}\Omega$ ,  $M_0=10\,{\rm k}\Omega$ , and  $D=10\,{\rm nm}$ . There is an obvious turning point at  $C_4$  in  $q-\varphi$  curve.

#### 3. The Memristive Delayed System

In this section, we design a delayed chaotic system with memristors, which is described by the following first-order delay differential equation:

$$\dot{x}(t) = ax(t) + b F(x(t-\tau)) + c, \tag{3.1}$$

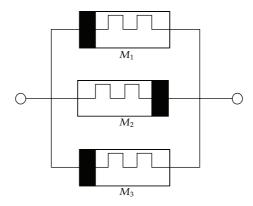

Figure 3: The parallel circuit of three memristors.

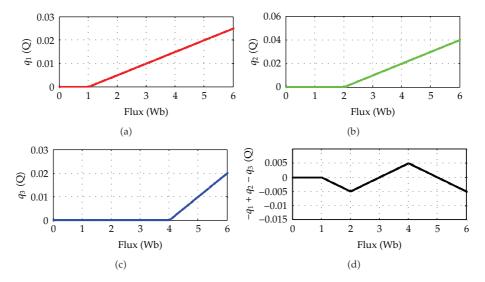

**Figure 4:** The curves of  $q - \varphi$  relation in the memristive parallel system.

where  $\tau$  is a delay time, a, b, and c are system parameters, and F[] is a nonlinear function composed by three memristors.

From Section 2, we can find  $q-\varphi$  characteristics of memristor are determined by four internal parameters ( $R_{\rm ON}$ ,  $R_{\rm OFF}$ ,  $M_0$ , and D) described by (2.3). If we adjust the turning point and the segment's slope, the combinational circuit of memristors can implement a piecewise function through the original point. The parallel circuit of three memristors is shown in Figure 3. The parameters of memristors are set as follows:  $R_{\rm OFF1} = R_{\rm OFF2} = R_{\rm OFF3} = 100 \, \rm k\Omega$ ,  $D_1 = D_2 = D_3 = 10 \, \rm nm$ ,  $R_{\rm ON1} = 200 \, \Omega$ ,  $R_{\rm ON2} = R_{\rm ON3} = 100 \, \Omega$ ,  $M_{01} = 10 \, \rm k\Omega$ ,  $M_{02} = 10 \, \rm k\Omega$ , and  $M_{03} = 10 \, \rm k\Omega$ . The simulation results are shown in Figure 4.

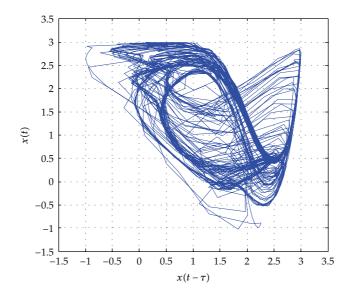

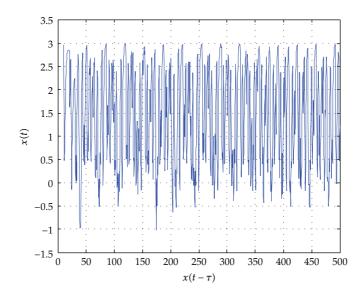

In the first-order delay differential equation (3.1), when a = -1, b = 1000, c = 3, and the delay time  $\tau = 10$ , there is a chaotic attractor in  $x(t) - x(t - \tau)$  plane (see Figure 5). The time series x(t) is exhibited in Figure 6.

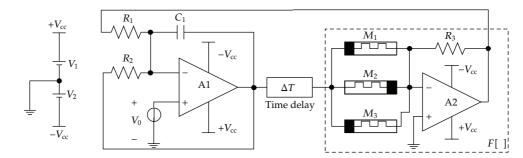

The circuitry implementation of the delayed memristive system: a possible electronic circuit realizing the system is given in Figure 7. The circuit consists mainly of three basic

Figure 5: A chaotic attractor of the delayed memristive system (3.1).

**Figure 6:** Time dependence of the state variables x(t) in the system (3.1).

blocks: the integrator (A1), the delay element (Time delay), and the nonlinear block (F[]). The electronic equation of system is

$$\frac{dv_x(t)}{dt} = -\frac{1}{R_2C}v_x(t) - \frac{1}{R_1C}F(v_x(t-\tau)) + \frac{(R_1 + R_2)V_0}{R_1R_2C}.$$

(3.2)

Figure 7: The circuitry implementation of memristive delayed system.

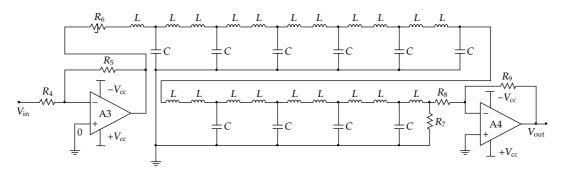

Figure 8: Circuit implementation of the time delay block.

The F[] block is composed of three memristors and an  $\mu$ A741 operational amplifier, which follows can be written as follows:

$$F(\varphi(t)) = -R_3 \left[ \frac{\varphi(t)}{-M_1(t)} + \frac{\dot{\varphi}(t)}{M_2(t)} + \frac{\varphi(t)}{-M_3(t)} \right]. \tag{3.3}$$

The time-delay circuit block (see Figure 8) is a network of T-type LCL filters with matching resistors, where n is the number of the LCL filter. The dimensionless delay parameter is

$$\tau = \frac{n\sqrt{2LC}}{R_0C_0}, \quad n \ge 1. \tag{3.4}$$

Notably, the T-type LCL unit will bring a little attenuation of the circuit gain. This hurdle can be easily eliminated by operational amplifiers A3 and A4. The circuit parameters are set as follows:  $R_0 = 1 \,\mathrm{k}\Omega$ ,  $C_0 = 100 \,\mathrm{nF}$ ,  $L = 9.5 \,\mathrm{mH}$ ,  $C = 525 \,\mathrm{nF}$ , n = 10,  $R_6 = R_7 = 1 \,\mathrm{k}\Omega$ ,  $R_4 = R_5 = R_8 = 10 \,\mathrm{k}\Omega$ , and  $R_9 = 30 \,\mathrm{k}\Omega$ . According to (3.4), we can get  $\tau = 10$ .

Set  $R_1 = 1 \text{ k}\Omega$ ,  $R_2 = 1 \text{ k}\Omega$ ,  $R_3 = 1 \text{ M}\Omega$ ,  $C_1 = 1 \mu\text{F}$ , and  $V_1 = V_2 = 15 \text{ V}$ , system (3.2) has a chaotic attractor in  $x(t) - x(t - \tau)$  plane as sown in Figure 5.

#### 4. Conclusion

This paper gives a new perspective to understand the performance and application of memristor. The proposed piecewise models are composed by three memristors. We can that find memristor can remember not only the charge (current) but also magnetic flux (voltage). As the nonlinear element, the memristor can also act as an essential nonlinear part in chaotic system. The SPICE models designed in this paper can complete a good simulation work of chaotic circuits, which are expected to produce more rich chaotic attractors.

## Acknowledgments

The work was supported by the National Natural Science Foundation of China under Grants 60972155 and 61101233, the Natural Science Foundation of Chongqing under Grants CSTC2009BB2305, the Fundamental Research Funds for the Central Universities under Grant XDJK2012A007 and XDJK2010C023, the University Excellent Talents supporting Foundations in of Chongqing under Grant 2011-65, the University Key teacher supporting Foundations of Chongqing under Grant 2011-65, the National Science Foundation for Post-doctoral Scientists of China under Grant CPSF20100470116, the Doctoral Foundation of the Southwest University under Grant SWUB2008074, and Spring Sunshine Plan Research Project of Ministry of Education of China under Grant z2011148.

#### References

- [1] L. O. Chua, "Memristor—the missing circuit element," *IEEE Transactions on Circuit Theory*, vol. 18, no. 5, pp. 507–519, 1971.

- [2] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7250, pp. 80–83, 2009.

- [3] E. M. Drakakis, S. N. Yaliraki, and M. Barahona, "Memristors and Bernoulli dynamics," in *Proceedings* of the 12th International Workshop on Cellular Nanoscale Networks and Their Applications (CNNA '10), February 2010.

- [4] G. Q. Zhong, K. F. Man, and G. Chen, "A systematic approach to generating n-scroll attractors," *International Journal of Bifurcation and Chaos*, vol. 12, no. 12, pp. 2907–2915, 2002.

- [5] M. Itoh and L. O. Chua, "Memristor oscillators," *International Journal of Bifurcation and Chaos*, vol. 18, no. 11, pp. 3183–3206, 2008.

- [6] C. Li, M. Wei, and J. Yu, "Chaos generator based on a PWL memristor," in *Proceedings of the International Conference on Communications, Circuits and Systems (ICCCAS '09)*, pp. 944–947, July 2009.

- [7] Z. H. Lin and H. X. Wang, "Image encryption based on chaos with PWL memristor in Chua's circuit," in *Proceedings of the International Conference on Communications, Circuits and Systems (ICCCAS '09)*, pp. 964–968, July 2009.

- [8] B. Muthuswamy and P. Kokate, "Memristor-based chaotic circuits," *IETE Technical Review*, vol. 26, no. 6, pp. 417–429, 2009.

- [9] W. Sun, C. Li, and J. Yu, "A simple memristor based chaotic oscillator," in *Proceedings of the International Conference on Communications, Circuits and Systems (ICCCAS '09)*, pp. 952–954, July 2009.

- [10] D. Wang, H. Zhao, and J. Yu, "Chaos in memristor based Murali-Lakshmanan-Chua circuit," in Proceedings of the International Conference on Communications, Circuits and Systems (ICCCAS '09), pp. 958–960, July 2009.

- [11] L. D. Wang, E. M. Drakakis, S. K. Duan, P. F. He, and X. F. Liao, "Memristor model and its application for Chaos generation," *International Journal of Bifurcation and Chaos*, vol. 22, no. 8, 2012.